Delivering a sustainable future for UK printable electronics

Funded by the NorthWest Development Agency (NWDA), the collaborative project had interests in the development of novel designs and processes for organic circuits for integration with other components such as organic light-emitting diodes (OLED) for added functionalities.

Lead: Dr M Raja

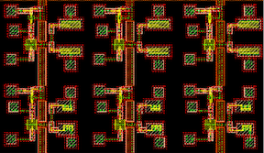

The size of the world market depends, on the one hand, on the range of functions the technology can produce, but also on the ability to scale-down device sizes and thereby enhance the yield of working devices: reducing cost whilst increasing circuit speed and system performance. The project was in collaboration with PETEC (Sedgefield) and OMIC (Manchester). Within the project, Liverpool developed a ‘sef-aligned’ gate for developing organic devices and circuits with layouts at indicated in figure 1 below.

Figure 1 - Example of layouts of simple circuit layouts of the self-aligned gate process.